# INSTRUCTION MANUAL

Control Unit

Model 780

©COPYRIGHT 1975 KEITHLEY INSTRUMENTS, INC.

FIRST PRINTING, NOV. 1975, CLEVELAND, OHIO, U.S.A. DOCUMENT NO. 27444, REVISION CODE AA.

• -

CONTENTS

| Section                                          | Page             |

|--------------------------------------------------|------------------|

| CONTENTS                                         | i i              |

| ILLUSTRATIONS.                                   | <br>             |

| SPECIFICATIONS                                   | i i i            |

| 1. GENERAL INFORMATION.                          | 1-1              |

| 1-1. GENERAL INFORMATION.                        | 1-1              |

| 1-2. WARRANTY INFORMATION                        | 1-1              |

| 1-3. CHANGES.                                    | • •              |

| 2. INITIAL PREPARATION.                          | 1-1              |

|                                                  | 2-1              |

|                                                  | 2-1              |

| 2-2 EVETEN CONCLOEDATIONS                        | 2-1              |

|                                                  | 2-1              |

|                                                  | 2-1              |

|                                                  | 2-2              |

| 2_7 - 4017 TO UCE DEAD DAVEL AANVEAMADA          | 2-2              |

| 2 INTEREACE CONCERENTIANO                        | 2-5              |

| 3-1. GENERAL                                     | 3-1              |

|                                                  | 3-1              |

|                                                  | 3-1              |

|                                                  | 3-3              |

|                                                  | 4-1              |

|                                                  | 4-1              |

|                                                  | 4-1              |

| 4-3. HOW TO INTERPRET THE FRONT PANEL INDICATORS | 4-6              |

| 5. MAINTENANCE                                   | 5-1              |

| 5-1. GENERAL.                                    | 5-1              |

| 5-2. REQUIRED TEST EQUIPMENT                     | 5-1              |

| 5-3. PERFORMANCE VERIFICATION                    | 5 <del>-</del> 1 |

| 6. ACCESSORIES                                   | 6-1              |

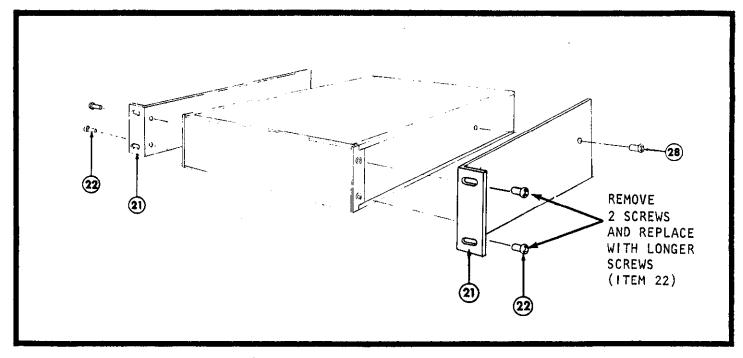

| 6-1. RACK MOUNTING KIT.                          | 6-1              |

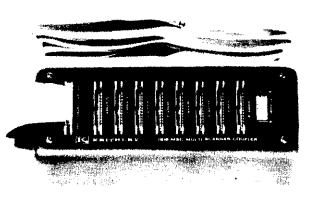

| 6-2. MULTI-SCANNER COUPLER (Model 7819-MSC)      | 6-2              |

| 6-3. INTERFACE EXTENDER CARD (Model 7819-IEC)    | 6-3              |

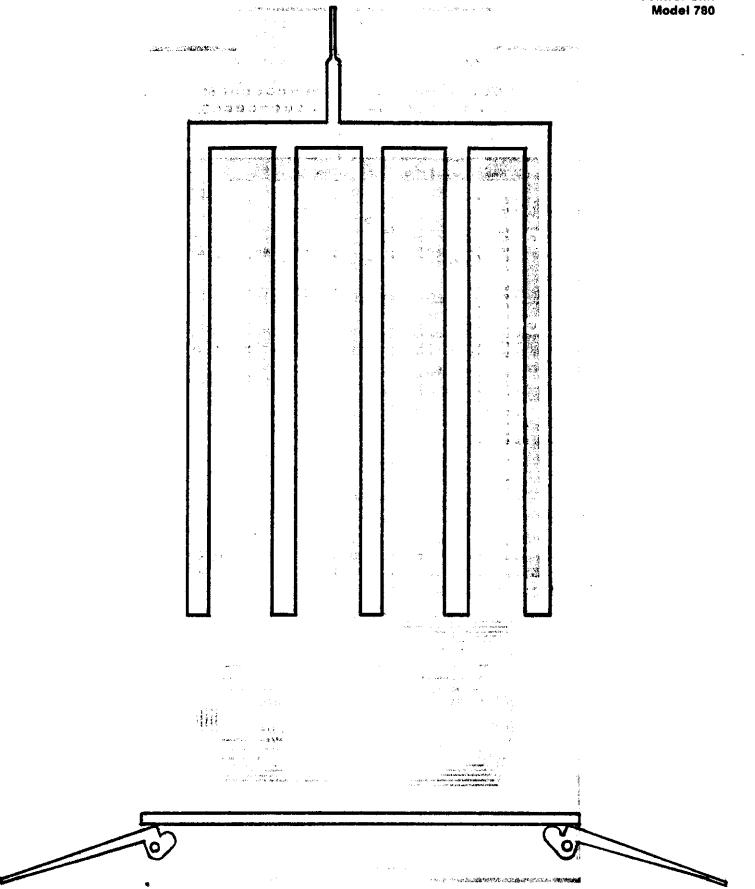

| 6-4. CUSTOM INTERFACE (Model 7802-CIK).          | 6-4              |

| 6-5. DUAL CONTROL UNIT COUPLER (Model 7819-DCC)  | 6-5              |

| 7. REPLACEABLE PARTS                             | 7-1              |

|                                                  | 7 <del>-</del> 1 |

|                                                  | 7-1              |

|                                                  | 7-1              |

|                                                  | f = 1            |

|                                                  |                  |

|                                                  |                  |

|                                                  |                  |

••

-

ILLUSTRATIONS

| igure<br>lo. | Title                                                       |   |

|--------------|-------------------------------------------------------------|---|

| 0.           |                                                             |   |

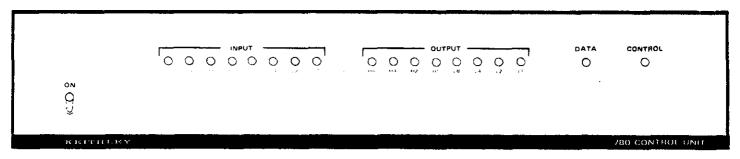

| 1            | Front Panel                                                 | 1 |

| 2            | Rear Panel                                                  | 1 |

| 3            | Installation of Series 7801, 7802, 7819-IEC and 7813 Cards. | 2 |

| 4            | Installation of Dual Control Unit Coupler (Model 7819-DCC)  | 2 |

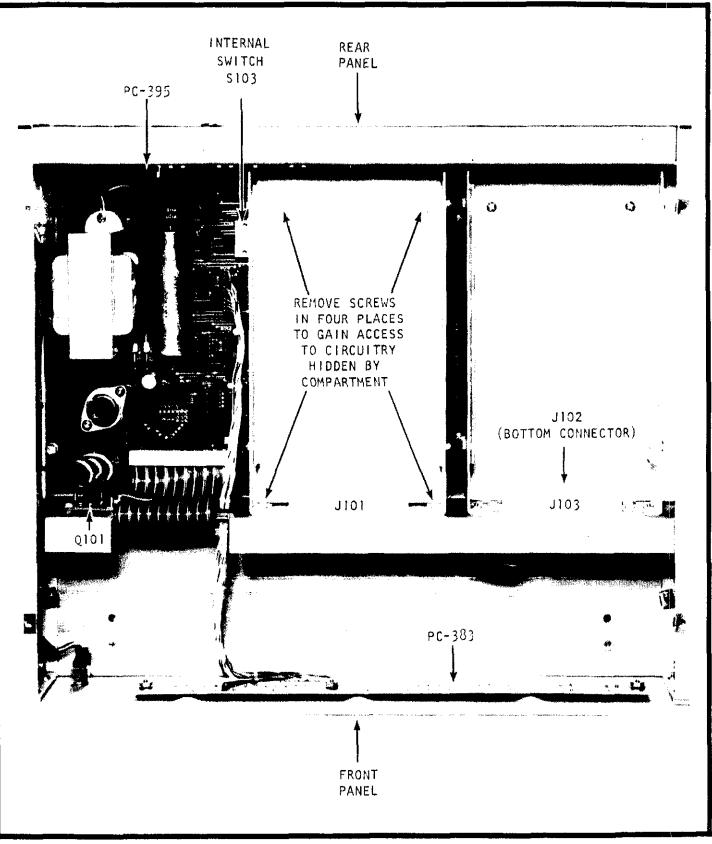

| 5            | Top View of Control Unit With Cover Removed                 | 2 |

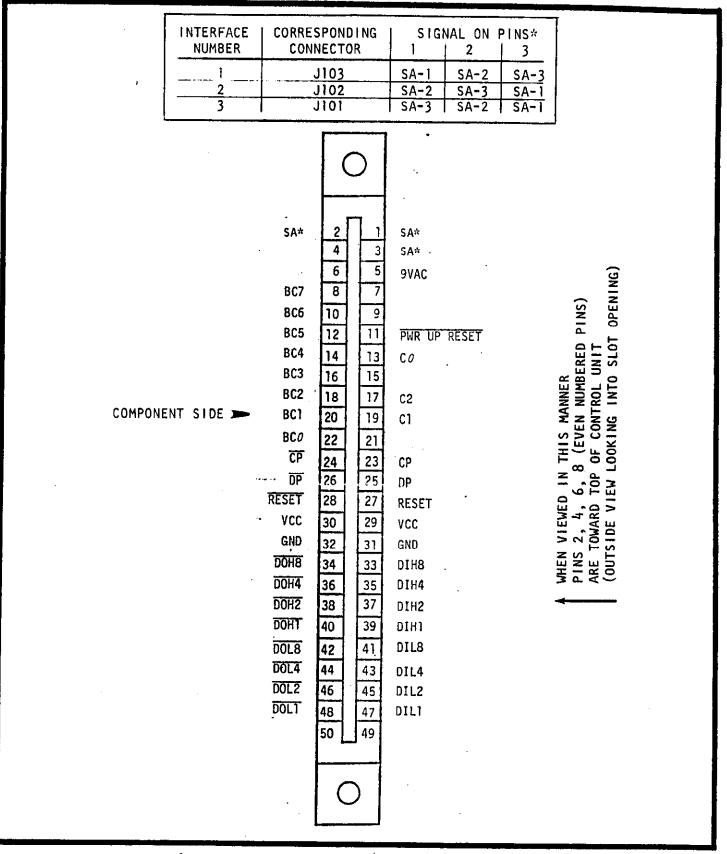

| 6            | Card-edge Connector (J101, J102, or J103)                   | 3 |

| 7            | Scanner Connector (P110)                                    | 3 |

| 8            | Front Panel Indicators                                      | L |

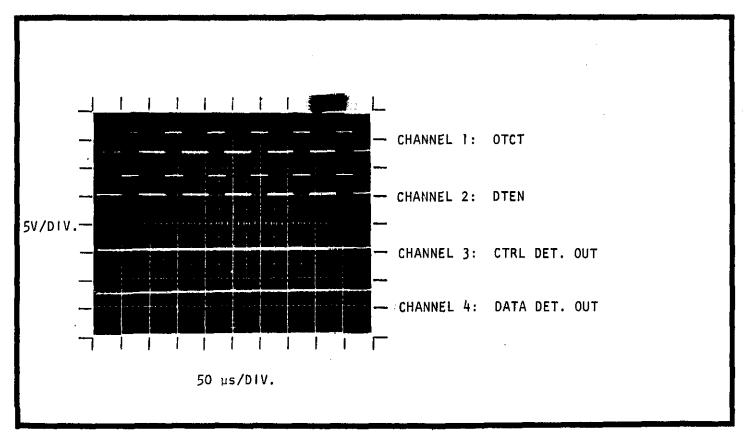

| 9            | Trace for Test #1                                           | 5 |

| 10           | Trace For Test #2                                           | 5 |

| 11           | Trace For Test #3                                           | 5 |

| 12           | Trace For Test #4                                           | ġ |

| 13           | Trace For Test #5                                           | 5 |

| 14           | Trace For Test #6                                           | 5 |

| 15           | Trace For Test #7                                           | 5 |

| 16           | Trace For Test #10                                          | 5 |

| 17           | Trace For Test #11                                          | 5 |

| 18           | Trace For Test #13                                          | 5 |

| 19           | Trace For Test #14                                          | 5 |

| 20           | Trace For Test #15                                          | 5 |

| 21           | Trace For Test #16                                          | 5 |

| 22           | Trace For Test #19                                          | 5 |

| 23           | Trace For Test #20                                          | 5 |

| 24           | Trace For Test #21                                          | 5 |

| 25           | Trace For Test #22                                          | 5 |

| 26           | Rack Mounting of the Control Unit                           | 6 |

| 27           | Multi-Scanner Coupler (Model 7819-MSC)                      | 6 |

| 28           | Typical System 1 Multi-Scanner Connection                   | 6 |

| 29           | Custom Interface (Model 7802-CIK)                           | 6 |

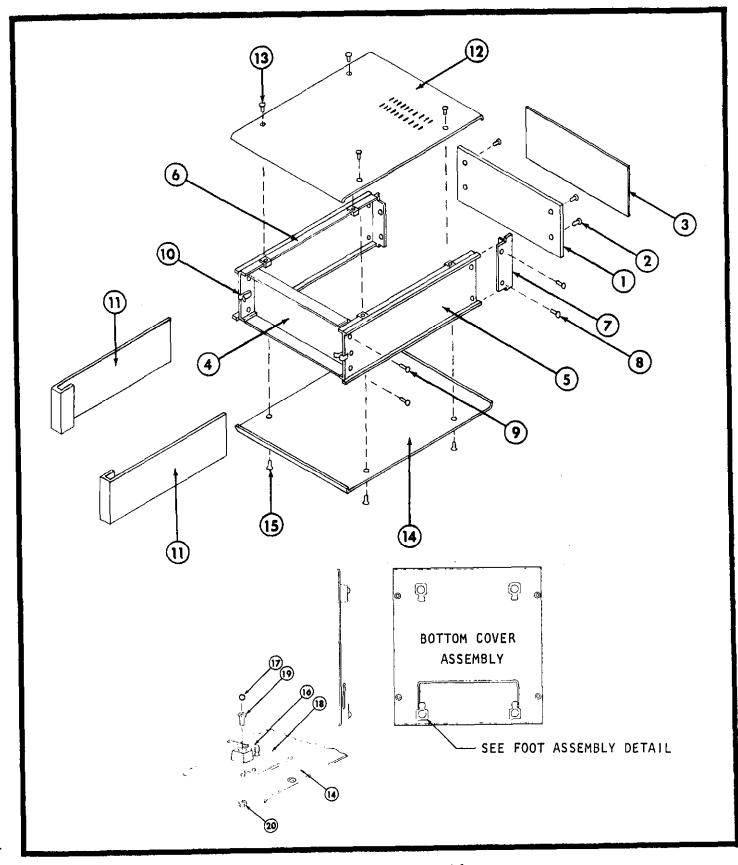

| 30           | Chassis Assembly                                            | 7 |

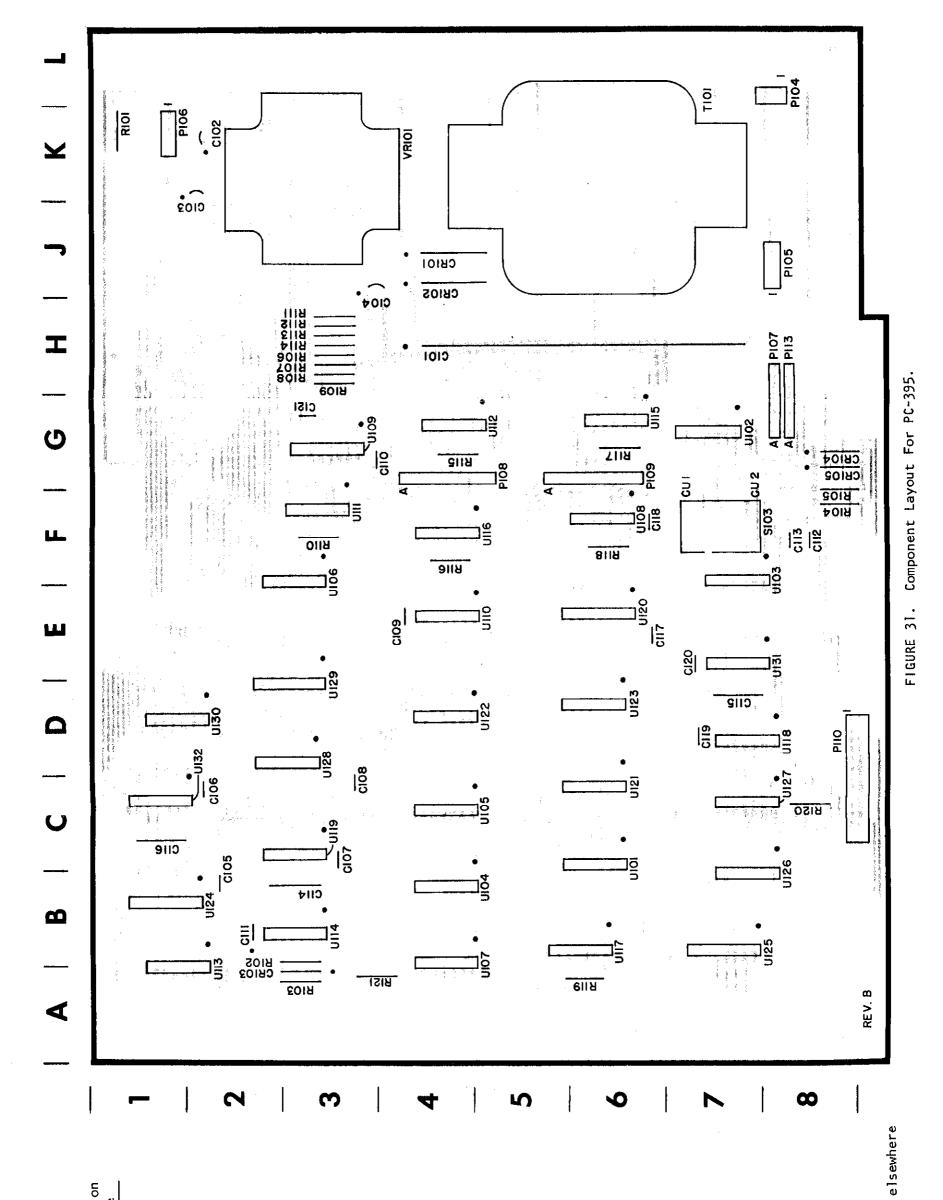

| 31           | Component Layout For PC-395                                 | 7 |

|              |                                                             |   |

|              | ·                                                           |   |

|              |                                                             |   |

|              |                                                             |   |

|              |                                                             |   |

|              |                                                             |   |

|              |                                                             |   |

|              |                                                             |   |

|              |                                                             |   |

|              |                                                             |   |

|              |                                                             |   |

|              |                                                             |   |

#### SPECIFICATIONS

GENERAL: Holds up to three System 1 Instrument Interface or special-purpose cards. Supplies power to cards. Captive cable plugs directly into the System 1 Programmable Calculating Unit. DISPLAY: 18 LED lamps indicate the last Output 8-bit word transferred, the next 8-bit word to be input, and whether the last word transferred was Data or Control. CONTROLS: Front panel power switch. Internal switch sets Control Unit address. 702/702X INTERFACE: GENERAL: Built-in interface connects directly to one Model 702/702X 10channel Scanner, or with 7819-MSC, to as many as eight 10-channel Scanners for random access to single channels. For parallel-channel or matrix operation, one channel on each Scanner may be selected. OUTPUT INSTRUCTION: Control Transfer: Deactivates all or selectively activates one of up to 80 channels. Power up/Reset: All scanner channels Off. Nominal Instruction Time: 70 milliseconds. ISOLATION (PCU GROUND TO ANALOG LO): Provided by Model 702X plug-in cards. ENVIRONMENT: OPERATING: 0°C to 40°C up to 80% relative humidity. STORAGE: -25°C to 80°C POWER: 90-110, 105-125, 210-250 volts (switch selected), 50-60 Hz, 50 watts. DIMENSIONS, WEIGHT: 3-1/2 in. full rack, overall bench size 4 in. high x 17-1/4 in. wide x 15-1/2 in. deep (105 x 440 x 395 mm); 5 ft. (1-1/2m) captive cable to PCU. Net weight, 13 pounds (5,8 kg). ACCESSORIES FURNISHED: Hardware for standard 3-1/2 in. x 19 in. rack mounting. 15-1/2 in. (395 mm) depth behind front panel.

#### SECTION 1. GENERAL INFORMATION

1-1. INTRODUCTION. The Model 780 Control Unit provides the link between the Programmable Calculating Unit (PCU) and all other instrumentation in the System 1. The Control Unit may be used with up to three Instrument Interfaces or other devices and eight Scanners. (A PCU and appropriate I/O Handler Software is needed to communicate with the Control Unit.)

Instrument Interfaces may be installed in any of three rear panel plug-in compartments or "slots". The locations of the Instrument Interfaces are labeled as Interface Number 1, 2, and 3.

Scanner interface circuitry is built into each Control Unit. The rear panel "SCANNER" connector mates with a System Interconnect Cable (Model 7021-2) furnished with the Keithley Model 702 Scanner.

When a Multi-Scanner Coupler is connected to the Control Unit, up to eight Scanners (80 channels total) may be used. Each Scanner connects to the MSC via individual System Interconnect Cables.

The Control Unit has 18 indicators on the front panel which display pertinent information as to the status of System 1 operations.

- •INPUT Indicators: These indicators represent an 8-bit word to be transferred from the Control Unit to the PCU.

- •OUTPUT Indicators: These indicators represent an 8-bit word which has been transferred from the PCU.

•DATA Indicator: This indicator identifies the last 8-bit word transferred as DATA. •CONTROL Indicator: This indicator identifies the last 8-bit word transferred as a CONTROL byte.

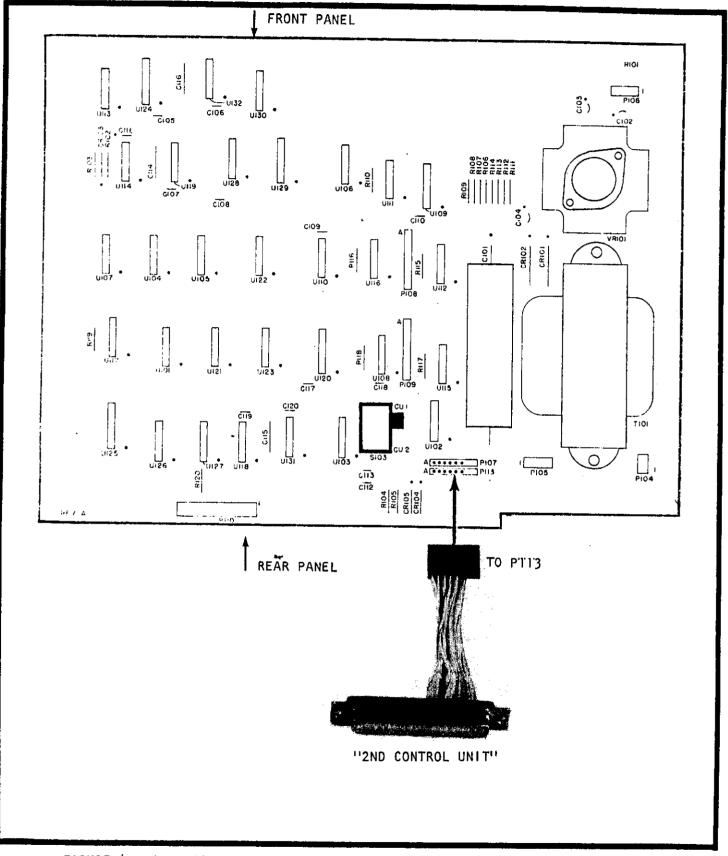

In a System 1/782-XY, two Control Units are used. In this configuration an internal switch on each Control Unit is used to identify Control Unit #1 (CU1) and Control Unit #2 (CU2) in the System. This identification enables the user to communicate to either Control Unit via 1/O Handler Software. A Dual Control-Unit Coupler must be installed on either Control Unit CU1 or CU2 to facilitate connection of a second Control Unit. The Control Units may be rack mounted using hardware furnished. The captive cable on the Control Unit is five feet long and mates with a 37-pin connector on the PCU or 2nd Control Unit. Cabling to instrument or other devices is furnished with individual Instrument Interfaces.

1-2. WARRANTY INFORMATION. See GUIDE TO USING THE SYSTEM 1 for detailed information.

1-3. CHANGES. Improvements or changes to the Control Unit which are not incorporated into the *INSTRUCTION MANUAL* can be found in the System | *Instruction Manual Addenda*.

SECTION 1

|    | · • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |            |        |    | 1    |         |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------|--------|----|------|---------|

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |            |        |    |      |         |

|    | 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.111 1.1111 1.111 1.111 1.111 1.1111 1.1111 1.1111 1.1111 1.1111 1.1111 1.1111 1.1111 1.1111 1.1111 1.1111 1.1111 1.1111 1.1111 1.1111 1.111111 | ······································ | <u>г</u> ш | AFPLAT | ·  | UATA | CONTROL |

| ON | anthe construction of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | • J .                                  |            |        |    |      |         |

| Ø  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |            |        |    |      |         |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        | ····       |        | ·· |      |         |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        |            |        |    |      |         |

FIGURE 1. Front Panel.

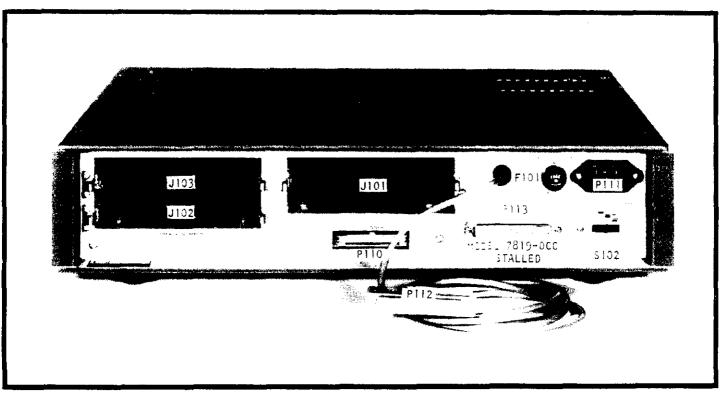

FIGURE 2. Rear Panel.

٠

#### SECTION 2. INITIAL PREPARATION

2-1. GENERAL. This section provides information needed for incoming inspection and preparation for use.

2-2. INSPECTION. The equipment furnished was carefully inspected both mechanically and electrically before shipment. Upon receiving the equipment, check for obvious damage which may have occured during transit. Report any damage to the shipping agent and your Keithley representative.

2-3. SYSTEM CONSIDERATIONS. The Control Unit is used in all configurations of the System 1 Calculator-Based instrumentation System. It is recommended that the user determine the configuration to be used prior to placing the Control Unit in the System. The following factors should be considered:

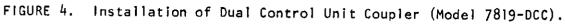

<u>a.</u> Use of more than one Control Unit. The Control Unit has an internal switch (S103) which is set at the factory in CUI position, to designate the Control Unit as "Control Unit 1". If two Control Units are to be used in the System 1, the Dual Control-Unit Coupler must be incorporated and the second Control Unit must be designated as CU2. If only one Control Unit is used, no modification of the Control Unit is needed. See Figure 5 for location of internal switch S103.

TABLE 2-1.

| <br>             |                                   |                               |                                   |         |

|------------------|-----------------------------------|-------------------------------|-----------------------------------|---------|

| Model No.        | Number of Control<br>Units Needed | Dual Control-<br>Unit Coupler | S103 Setting                      |         |

| <br>System 1/781 | 1                                 | Not Required.                 | CUI                               | <u></u> |

| System 1/782     | 2                                 | Required.<br>See Table 2-4.   | First unit-CUl<br>Second unit-CU2 |         |

Control Unit Useage in System 1

b. Use of two or more Scanners. If two or more Scanners are to be used in the System 1, the Multi-Scanner Coupler must be used with the Control Unit. (See page 6-2.)

c. Use of more than one Instrument Interface. If more than one Instrument Interface is installed in a Control Unit at the same time, Model 7820-GPA I/O Handler Software must be used. See *GUIDE TO USING THE SYSTEM 1* for system hardware and software requirements.

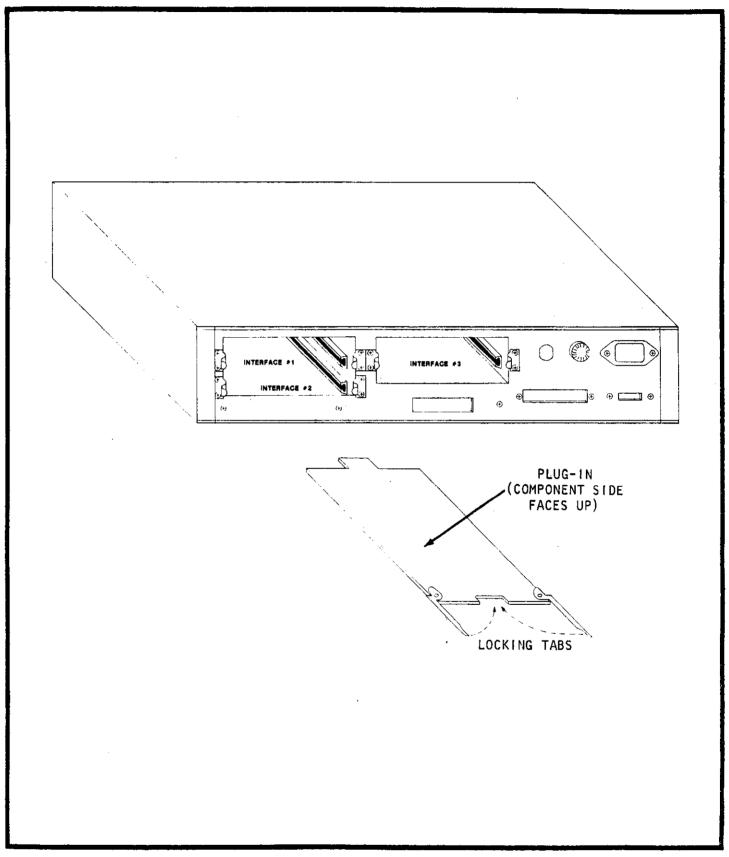

2-4. HOW TO INSTALL INTERFACES. (SERIES 7801, 7802, 7813)

<u>a.</u> Locations. The rear panel of the Control Unit has three plug-in compartments, identified as Interface Numbers 1, 2, and 3. These compartments can accept any Keithley Instrument Interface or Accessory listed in Table 2-2.

ł

#### TABLE 2-2.

Instrument Interfaces and Accessories Useable in the System 1

| Model No.             | Name                         |

|-----------------------|------------------------------|

| Model 7801-1608/16028 | Instrument Interface         |

| Model 7801-171/1712   | Instrument Interface         |

| Model 7801-180/1802   | Instrument Interface         |

| Model 7801-445        | Instrument Interface         |

| Model 7801-616/6162   | Instrument Interface         |

| Model 7802-110        | 8-Bit Isolated 1/0 Interface |

| Model 7813            | Interval Timer/Clock         |

| Model 7802-C1K        | Custom Interface Card        |

| Model 7819-1EC        | Interface Extender Card      |

b. Installation. Any Keithley System 1 Interface will mate with any of the three plug-in compartments. Slide the Plug-in Card into the compartment with "component side" facing up. Make certain the card edges are aligned with the grooves in the compartment. When the card is fully inserted, the "locking tabs" on the card should be snapped into locking position as shown in Figure 3. On some Instrument Interfaces a switch setting must be made on the pc card prior to installing in the Control Unit. (See INSTRUCTION MANUAL, Instrument Interface.)

c. Removal. Unfasten "locking tabs" by pulling both tabs outward. Grasp the end of the card and pull out of chassis.

2-5. HOW TO RACK MOUNT THE CONTROL UNIT. The Control Unit is designed for 19 inch full rack mounting when used with the Model 1007 Rack Mounting Kit. The position of the Control Unit in a rack should be determined relative to the instruments or devices used in the System 1. For example, Series 7801 Instrument Interfaces have a 6 foot (2m) length cable which mates with a digital measuring instrument. Therefore considerations should be made for cable routing behind the rear panel. See page 6-1 for rack mounting information.

2-6. HOW TO APPLY POWER TO THE CONTROL UNIT.

a. How to set the Line Switch. The Control Unit has a single Line Switch which permits the user to select line voltage in three ranges. See Table 2-3.

CAUTION

Remove line cord before changing switch positions.

#### TABLE 2-3.

Line Voltage Selection

| Position | Line Voltage | Fuse (Keithley Part No.) |

|----------|--------------|--------------------------|

| (`       | 90-110V rms  | 1/2A (FU-4)              |

|          | 105-125V rms | 1/2A (FU-4)              |

|          | 210-250V rms | 1/4A (FU-17)             |

b. Line Power. The Control Unit line power receptacle mates with Keithley line cord CO-7 (furnished). The line cord is designed for use with three-prong receptacles having a grounded connection.

FIGURE 3. Installation of Series 7801, 7802, 7819-IEC and 7813 Cards.

AA

SECTION 2

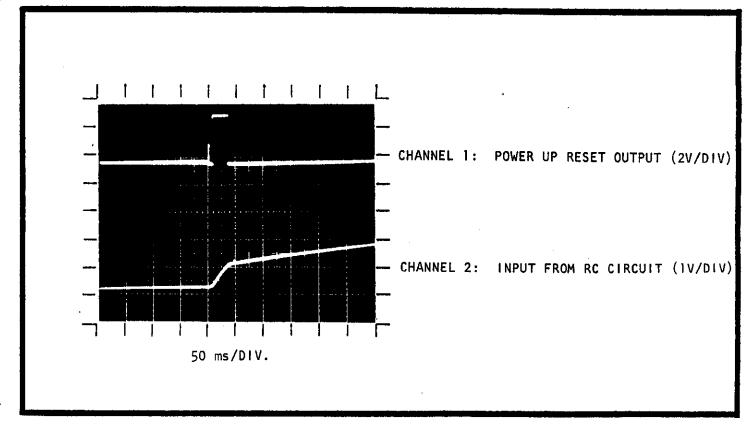

<u>c.</u> Power-Up Reset. When power is applied to the Control Unit a "Power-Up" reset is generated which causes all installed interfaces to go to their specific "power up" condition. The "power up" condition is listed in *INSTRUCTION MANUAL*, *Instrument Interface*, Series 7801, 7802 or 7813.

2-7. HOW TO USE REAR PANEL CONNECTORS (See Figure 2).

a. SCANNER Connector (P110). This connector is a 26-pin 3M Electro Products Division Part No. 3429. Pin 4 has been removed to admit a "polarizing key" on the mating System Interconnect Cable (Model 7021-2 or 7021-10).

b. TO PCU Cable (P112). This five foot long cable is a 37-conductor integrally mounted cable terminated by an ITT Cannon Part No. DC-37P male connector. The cable mates with a receptacle on Keithley PCU, Peripheral Coupler, or second Control Unit.

c. 2ND CONTROL UNIT (Spare opening). This opening is used when modifying a Control Unit for use in a System 1/782. When shipped from the factory the Control Unit has a cover plate (part no. 26864) over the opening. When a Dual Control-Unit Coupler is installed on the Control Unit the cover plate must be removed and replaced with a 37-pin receptacle. See Table 2-4 and Figure 4.

d. INTERFACE NUMBER 1 (J103). This connector is a 50-pin card-edge type which mates with Series 7801 and 7802 Instrument Interfaces and Model 7813.

e. INTERFACE NUMBER 2 (J102). This connector is a 50-pin card-edge type which mates with Series 7801 and 7802 Instrument Interfaces and Model 7813.

f. INTERFACE NUMBER 3 (J101). This connector is a 50-pin card-edge type which mates with Series 7801 and 7802 Instrument Interfaces and Model 7813.

#### TABLE 2-4.

How to Install the Dual Control-Unit Coupler

- 1. Disconnect power cord.

- 2. Remove cover plate over 2nd CONTROL UNIT opening.

- 3. Remove the Control Unit top cover.

- 4. Install 37-pin receptacle using original screws used with cover plate.

- 5. Install Berg housing (8-pin) as shown in Figure 4.

- 6. Replace top cover.

÷

FIGURE 5. Top View of Control Unit With Cover Removed.

#### SECTION 3. INTERFACE CONSIDERATIONS

3-1. GENERAL. This section provides basic operating information concerning the interface bus and Scanner interface.

3-2. INTERFACE BUS CONFIGURATION. The Control Unit has three 50-pin card-edge connectors J101, J102, and J103 corresponding to Interface Numbers 3, 2, and 1. Except for Slot Address lines, all signals are wired in parallel on the three connectors. See Figure 6.

Summary of Signals on Interface Bus

| Name                                             | Remarks                                                                                                                                       |  |  |  |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Slot Address (SA)                                | All three Slot address lines are wired to connectors J101, J102, and J103. Refer to Figure 6 for wiring.                                      |  |  |  |

| 9VAC                                             | This voltage is an auxiliary ac voltage used for certain instrument interfaces.                                                               |  |  |  |

| PWR UP RESET                                     | This signal is generated when power is applied to the Control Unit.                                                                           |  |  |  |

| C <i>O</i> , Cl, C2                              | These signals are Control commands.                                                                                                           |  |  |  |

| CP (Control Pulse)                               | This signal is generated after a Control Byte has been received.                                                                              |  |  |  |

| DP (Data Pulse)                                  | This signal is generated after a Data Byte has bee transferred.                                                                               |  |  |  |

| RESET                                            | This signal is generated for either of the follow-<br>ing conditions:<br>RESET code is received from the PCU                                  |  |  |  |

|                                                  | PWR UP RESET is generated                                                                                                                     |  |  |  |

| vcc                                              | This is a +5V logic supply for Interface logic.                                                                                               |  |  |  |

| GND                                              | This is a logic supply "LO".                                                                                                                  |  |  |  |

| DIH8, DIH4, DIH2, DIH1<br>DIL8, DIL4, DIL2, DIL1 | These lines are the eight input data lines. Data which is to be sent to the PCU is applied to these lines.                                    |  |  |  |

| BC7, BC6, BC5, BC4,<br>BC3, BC2, BC1, BC0        | These lines are outputs of the Byte Counter circuit.                                                                                          |  |  |  |

| CP (Control Pulse)                               | See CP above.                                                                                                                                 |  |  |  |

| DP (Data Pulse)                                  | See DP above.                                                                                                                                 |  |  |  |

| RESET                                            | See RESET above.                                                                                                                              |  |  |  |

| DOH8, DOH4, DOH2, DOHT                           | These lines are the eight data output lines. These<br>lines represent data at the Output Register, except<br>that the data has been inverted. |  |  |  |

ł

+

**SECTION 3**

## INSTRUCTION MANUAL Control Unit

Model 780

FIGURE 6. Card-edge Connector (J101, J102, or J103).

3-2

ΔΔ

3-3. SCANNER INTERFACE. The Scanner interface provides capability to control up to 8 Keithley Model 702/702X Scanners. The "SCANNER" connector is a 26-pin connector that mates with a Series 7021 System Interconnect Cable. When used with a single Scanner, only one System Interconnect Cable is needed. If two or more Scanners are to be connected to a single Control Unit, a Multi-Scanner Coupler must be connected to the Control Unit. See Section 6, ACCESSORIES for detailed information on the use of the Multi-Scanner Coupler (Model 7819-MSC).

TABLE 3-2.

| Pin No.          | Name           | Remarks                         |

|------------------|----------------|---------------------------------|

| 1                | CHAD 1         | CHannel ADdress Input           |

| 2                | CHAD 4         | CHannel ADdress Input           |

| 3                | Not Used       | No Connection                   |

| 4                | Polarizing Pin | No Connection                   |

| 3<br>4<br>5<br>6 | LOCHAD 6       | LOad CHannel ADdress-Scanner #6 |

|                  | LOCHAD 7.      | LOad CHannel ADdress-Scanner #7 |

| 7                | LOCHAD 8       | LOad CHannel ADdress-Scanner #8 |

| 8                | RELAY READY    |                                 |

| 9                | REMOTE ALL OFF |                                 |

| 10               | Not Used       | No Connection                   |

| 11               | Not Used       | No Connection                   |

| 12               | LOCHAD 2       | LOad CHannel ADdress-Scanner #2 |

| 13               | LOCHAD 4       | LOad CHannel ADdress-Scanner #4 |

| 14               | CHAD 2         | CHannel ADdress Input           |

| 15               | CHAD 8         | CHannel ADdress Input           |

| 16               | LOCHAD 1       | LOad CHannel ADdress-Scanner #1 |

| 17               | Not Used       | No Connection                   |

| · 18             | COMMON         | Digital Common                  |

| 19               | COMMON         | Digital Common                  |

| 20               | COMMON         | Digital Common                  |

| 21               | COMMON         | Digital Common                  |

| 22               | COMMON         | " Digital Common                |

| 23               | Not Used       | No Connection                   |

| 24               | Not Used       | No Connection                   |

| 25               | LOCHAD 3       | LOad CHannel ADdress-Scanner #3 |

| 26               | LOCHAD 5       | LOad CHannel ADdress-Scanner #5 |

|                  |                |                                 |

|                  |                | PIN REMOVED AT 4                |

|                  |                |                                 |

|                  |                |                                 |

Connector (PIIO) Pin Identification on the Control Unit

FIGURE 7. Scanner Connector (P110) on Rear Panel.

## TABLE 3-3.

Typical Logic Definitions Based on Manufacturers' Data

| Input                    | Lines                    | Output                 | Lines                   |  |

|--------------------------|--------------------------|------------------------|-------------------------|--|

| LOGIC ''l''<br>(Minimum) | LOGIC ''O''<br>(Maximum) | LOGIC "1"<br>(Minimum) | LOGIC 'O''<br>(Maximum) |  |

| +2.0V                    | +0.8V                    | +2.4V                  | +0.4V                   |  |

NOTE

Absolute maximum input voltage = +5.25V Absolute minimum input voltage = -0.5V

TABLE 3-4.

.

Standard Terminology Used For Logic Lines

| Symbol Name | Definition | Comments         |

|-------------|------------|------------------|

| ABC         | High True  | True = Logic "1" |

| ABC         | Low True   | True = Logic "O" |

n 1.

#### SECTION 4. THEORY OF OPERATION

4-1. GENERAL. The Control Unit contains circuitry which links the Programmable Calculating Unit (PCU) and all other System 1 instrumentation. This circuitry handles data transfers between the PCU and accessory interfaces or the built-in scanner interface.

#### 4-2. CIRCUIT DESCRIPTION.

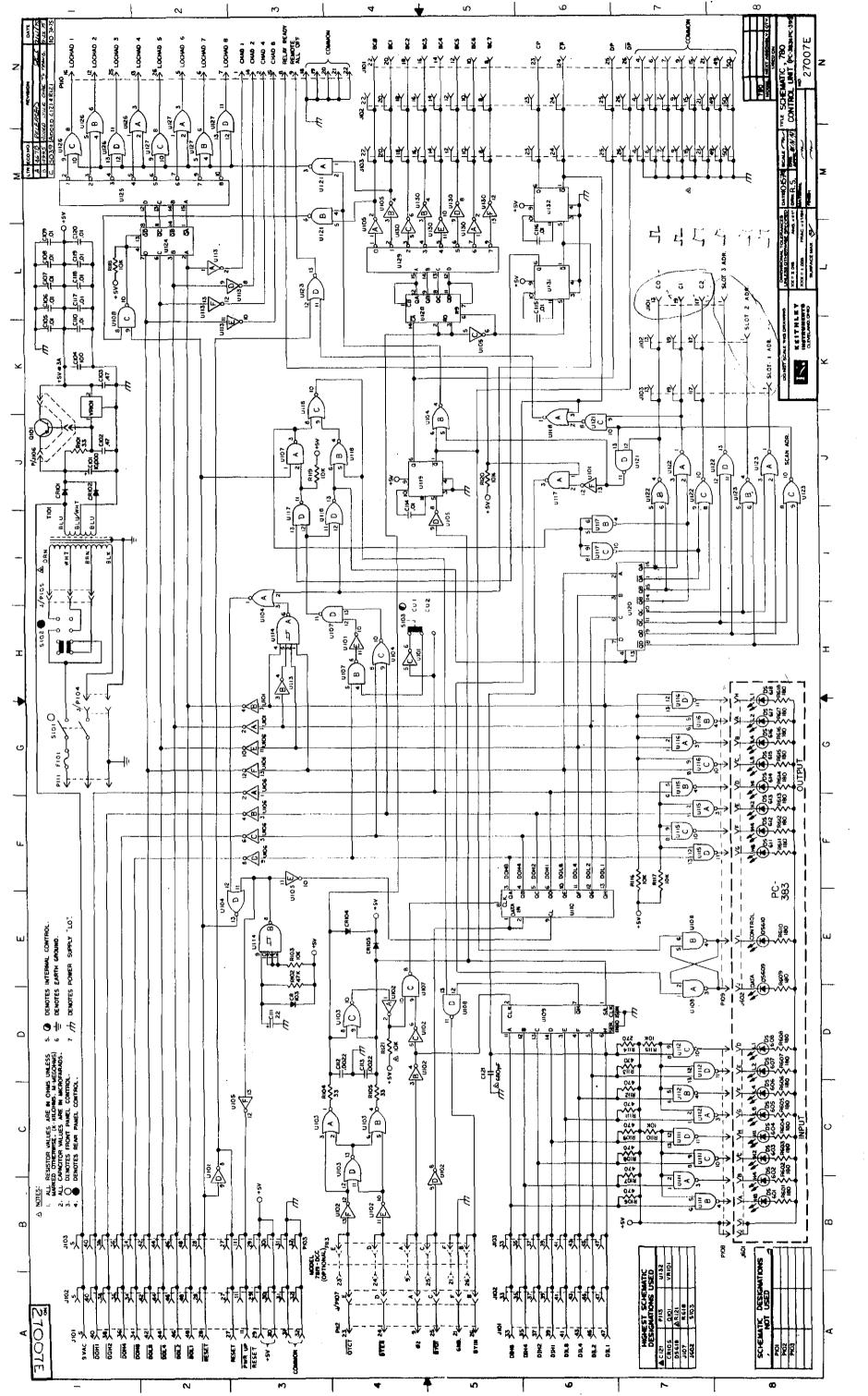

a. The circuitry can be divided into ten functional circuits.

- 1. Control/Data Byte Detector Circuit.

- 2. Output Control/Data Register Circuit.

- 3. Input Data Register Circuit.

- 4. Indicator Circuit.

- 5. Control Byte Decoder Circuit.

- 6. Reset Circuit.

- 7. Control Byte One-Shot Multivibrator Circuit.

- 8. Data Byte One-Shot Multivibrator Circuit.

- 9. Byte Counter Circuit.

- 10. Scanner Interface Circuit.

#### b. Control/Data Byte Detector Circuit.

1. General Circuit Description. This circuit indicates whether a Control Operation (OPCB) or Data Operation (OPDB, IPDB) is being executed. Input signals are OTCT and DTEN.

2. Detailed Circuit Description. When neither Control or Data operations are executed, OTCT and DTEN are a logic "O" during T8 to T15 of a machine cycle. When an OPCB instruction is executed, OTCT is at logic "1" during the entire machine cycle. When either an OPDB or IPDB instruction is executed, DTEN will remain a logic "1" for the entire machine cycle (i.e. DTEN will not have a transition from logic "1" to logic "O").

#### c. Output Control/Data Register Circuit.

1. General Circuit Description. This circuit is a serial in/parallel out Shift Register. Output control/data from the PCU is loaded into this register (U110) and clocked by  $\phi 2$ . BYOT is the serial input. BYOT is the inversion of signal BYOT.

2. Detailed Circuit Description. When an output instruction (OPCB or OPDB) is executed, the contents of the Index Register is shifted into the Output Register. Output lines DOLI through DOH8 are buffered and applied to the bus. If an OPCB instruction is executed the Control Byte Decoder is activated.

ΆA

÷

4-1

#### SECTION 4

#### d. Input Data Register Circuit.

1. General Circuit Description. This circuit is a parallel in/serial out Shift Register. Input data from the Control Unit is transferred to the PCU via this register. A byte (8 bits) of data is serially transmitted to the PCU via BYIN, and clocked by  $\phi 2$ .

2. Detailed Circuit Description. Data input lines on the bus (DILI through DIH8) are shifted into the PCU Index Register and replace previous contents.

#### e. Indicator Circuit.

1. General Circuit Description. A total of 18 LED indicators are used on the Control Unit front panel to display data or status of control operations. The indicators are grouped as follows:

a) INPUT indicators (L1 through H8). These indicators represent data to be transferred from the Control Unit to the PCU.

b) OUTPUT indicators (L1 through H8). These indicators represent data which has been transferred from the PCU.

c) INSTRUCTION indicators. These indicators show whether the last I/O instruction executed was a control operation (OPCB) or a data operation (OPDB or IPDB).

2. Detailed Circuit Description. All indicators are driven by two-input NAND gates.

a) INPUT indicators (L1 through H8). Input data to be shifted into the PCU Index Register is displayed on indicators L1 through H8.

b) OUTPUT indicators. The data on the Output Control/Data Register is displayed on indicators L1 through H8.

c) INSTRUCTION indicators. The NAND gates are connected to form an RS Flip-Flop. The R and S inputs to the Flip-Flop are the two outputs of the Control/Data Byte Detector.

#### f. Control Byte Decoder Circuit.

1. General Circuit Description. This circuit accepts control information and decodes it into individual control signals. These signals are then used for controlling or transferring data to accessory instruments (when appropriate accessory Instrument Interface is installed).

2. Detailed Circuit Description.

a) PCU peripherals and the Control Unit are addressed using IH of an OPCB. Since IH is four bits wide, there are sixteen possible addresses, 0 through 15. System 1 uses two of sixteen possible addresses. Addresses 8 (binary 1000) and 9 (binary 1001) are used to address CUI and CU2 respectively. The address to which a Control Unit will respond is determined by the setting of S103, located on the Control Unit printed circuit board.

b) As mentioned above, the contents of the Output Control/Data Register is a copy of the index Register after an output instruction has been executed. Of these outputs, DOH1 through DOH8 represent the contents of IH. Execution of an OPCB instruction enables these bits to be applied to an address decoder. This decoder determines whether IH contains an eight or a nine depending on the position of the S103. The decoder's output will go high if IH contains a "one of us" code.

c) The low-order four bits of a Control Byte represent an operation code. If the address contained in IH is "one of us", that is an eight or nine, the DOL1 through DOL8 data are latched into Ul20. The contents of IL are then decoded into Slot Addresses and Control signals. It is these signals which control the action of the instrument interface cards.

d) In addition to enabling the IL latch, the address decoder also sets an RS flipflop when IH contains a "one of us" code. The output of this flip-flop is used to enable BYIN so that data can be transferred to the PCU. When the address part of a Control Byte is not "one of us", the flip-flop is reset. This prevents our interface from interferring with other peripherals which might be connected to the PCU.

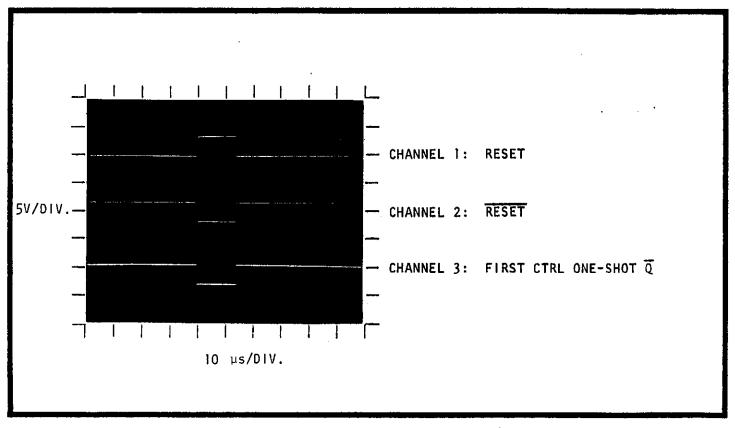

g. Reset Circuit.

1. General Circuit Description. A RESET signal is generated under the following conditions:

a) Control Unit Power Up. When power is first applied to the Control Unit via the Power Switch, or disconnecting and reconnecting line power to the Control Unit with Power Switch set to ON.

b) PCU Reset. When a RESET command is generated at the PCU.

2. Detailed Circuit Description.

a) Control Unit Power Up. The RESET signal is applied to the bus and causes the following actions:

1) Clears Output Data Register.

2) Sets all accessory instrument interface circuitry to "Power-Up" condition. (See individual instrument interface instruction Manual for detailed information.)

- 3) Clears control signals CO, Cl, and C2.

- 4) Disables BYIN (resets Flip-Flop).

- 5) Initiates a PWR UP RESET.

b) PCU Reset. When a RESET command (OPCB and  $IL = 13_{10}$ ) occurs, the following actions result:

1) Output Data Register =  $13_{10}$ .

2) Sets all accessory Instrument Interface circuitry to "Power-Up" condition. (See individual *INSTRUCTION MANUAL* for detailed information.)

- 3) Clears control signals CO, Cl, and C2.

- 4) Disables BYIN (resets Flip-Flop).

h. Control Byte One-Shot Multivibrator Circuits.

1. General Circuit Description. These circuits are used to synchronize transfer of control information within the Control Unit.

2. Detailed Circuit Description.

a) U131. This One-Shot is fired at a logic "1" to logic "0" transition of the Control Byte Detector signal. This occurs at T15 of an OPCB instruction. The One-Shot output enables the Address Decoder and Reset Command Detector.

b) U132. This One-Shot is fired at a logic "1" to logic "0" transition of the above one-shot and causes a Control Pulse (CP) on the bus.

#### i. Data Byte One-Shot Multivibrator Circuit.

1. General Circuit Description. The output of this circuit is called Data Pulse (DP). This signal is similar to CP.

2. Detailed Circuit Description (Ull9). This One-Shot is fired at a logic "1" to logic "0" transition of the Data Byte Detector signal, i.e. when either IPDB or OPDB operations are executed.

#### j. Byte Counter Circuit.

1. General Circuit Description. This circuit generates eight control signals, BCO through BC7, and are used as Strobe and Latch Enable functions.

2. Detailed Circuit Description. This circuit consists of a Decade Counter (U128) and a "One-out-of-Ten" Decoder (U129). When a Control Byte is detected, the Counter is reset to zero. The counter is incremented by DP. The Counter is wired so that when the counter is incremented beyond 7, the output is set to 9. The Byte Counter outputs are available on the bus, and permits data byte transfer without the need for a Control Byte Command (i.e. after an IPDB or OPDB instruction is executed, the Byte Counter is incremented, enabling the next data byte).

#### k. Scanner Interface Circuit.

1. General Circuit Description. This circuit contains logic to control one Scanner (or up to 8 Scanners, when the Multi-Scanner Coupler is used). The logic is divided into three functional circuits.

a) REMOTE ALL OFF Logic. When a REMOTE ALL OFF command is initiated by the PCU, the Scanner interface logic generates a logic "O" on pin 9 of SCANNER connector.

b) LOCHAD Logic. The LOCHAD logic latches a LOCHAD code coming from the PCU. A logic "O" is generated on the appropriate LOCHAD line.

c) CHAD Buffer Logic. These buffer stages provide fan-out drive capability.

2. Detailed Circuit Description.

a) REMOTE ALL OFF Logic. Three logic gates (U121C, U118A, U123D) are used to generate a REMOTE ALL OFF command. The specific logic requirements for activating REMOTE ALL OF are given in Table 4-1.

|              |    | INPU   | JT | OUTPUT |       |                                  |

|--------------|----|--------|----|--------|-------|----------------------------------|

| SCAN<br>ADDR | C1 | U121-8 | CP | U118-1 | RESET | REMOTE ALL OFF (Pin 9)           |

| 1            | 1  | 0      | 0  | 1      | 0     | O (REMOTE ALL OFF activated)     |

| )            | 1  | 0      | 1  | 0      | 0     | 1 (REMOTE ALL OFF not activated) |

| Х            | x  | X      | x  | X      | 1     | O (REMOTE ALL OFF activated)     |

| - T A I | BLE | - <i>h</i> = 1 |  |

|---------|-----|----------------|--|

| 1.01    |     |                |  |

| Logic | for | REMOTE                                  | ALL | OFF |

|-------|-----|-----------------------------------------|-----|-----|

|       |     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     |     |

X = Don't care

b) LOCHAD Logic. Five Logic gates are used with the Latch and Decoder. These gates control the operation of the latch and enable the LOCHAD buffers. Eight OR gates are used for buffering the LOCHAD outputs. When enabled, these gates apply the output of the decoder to the Scanners connected to the Control Unit.

c) CHAD Buffer Logic. The CHAD Buffer circuits (Ull3A, D, E, F) provide fan-out capability.

## TABLE 4-2.

LOCHAD Lines Used on Scanner Connector

| Scanner Number | Pin Number |

|----------------|------------|

|                | 16         |

| 2              | 12         |

| 3              | 25         |

| 4              | 13         |

| 5              | 26         |

| 6              | 5          |

| 7              | 6          |

| 8              | 7          |

## TABLE 4-3.

Logic for LOCHAD Lines

|               |   |         |    | OUTPUT |             |     |        |         |       |                            |

|---------------|---|---------|----|--------|-------------|-----|--------|---------|-------|----------------------------|

| S CAN<br>ADDR |   | U121-11 | DP | U104-4 | BC <i>O</i> | BC1 | U121-6 | U108-10 | RESET |                            |

| 1             | 1 | 0       | 0  | 1      | 1           | 0   | 0      | 1       | 1     | Latch enable is logic "]"  |

| 1             | 1 | 0       | 1  | 0      | 1           | 0   | 1      | 0       | 1     | Latch enable is logic "O"  |

| X             | X | X       | X  | Х      | Х           | X   | X      | X       | 0     | Latch enable is logic "!"  |

| 1             | 1 | 0       | 0  | 1      | 0           | 1   | 1      | 0       | 1     | Lochad enable is logic ""  |

| 1             | 1 | 0       | 1  | 0      | 0           | 1   | 1      | 0       | 1     | Lochad enable is logic "O" |

X = Don't care

TABLE 4-4.

Illustration of Logic for CHAD Lines (Four of Ten Useable Combinations Shown)

|   |      | I NP | UT   |      | OUTPUT |        |        |        |  |

|---|------|------|------|------|--------|--------|--------|--------|--|

|   | DOL8 | DOL4 | DOL2 | DOLI | CHAD 8 | CHAD 4 | CHAD 2 | CHAD 1 |  |

|   | 1    | 1    | 1    | 0    | 0      | 0      | 0      | 1      |  |

| • | 1    | 1    | 0    | 1    | 0      | 0      | 1      | 0      |  |

|   | 1    | 0    | 1    | 1    | 0      | 1      | 0      | 0      |  |

|   | 0    | 1    | 1    | 1    | 1      | 0      | 0      | 0      |  |

ł

|              | INPL       | JT      | OUTPUT                  |  |  |  |

|--------------|------------|---------|-------------------------|--|--|--|

| SCAN<br>ADDR | c <i>0</i> | U121-11 | U101-12                 |  |  |  |

| 1            | 1          | 0       | I (RELAY READY enabled) |  |  |  |

| 0            | 1          | 1       | 0                       |  |  |  |

| 1            | 0          | 1       | 0                       |  |  |  |

| 0            | 0          | 1       | 0                       |  |  |  |

TABLE 4-5.

| 4-3.  | HOW TO INTERPRET | THE FRONT | PANEL | INDICATORS. | The Contro | Unit has | 18 indicators as |  |

|-------|------------------|-----------|-------|-------------|------------|----------|------------------|--|

| shown | in Figure 8.     |           |       |             |            |          |                  |  |

INPUT. These indicators represent data to be sent to the PCU from Interface Number 1, 2, or 3 or Scanner interface.

OUTPUT. These indicators represent data which has been received from the PCU.

The data represented by the indicators is sometimes in the form of two 8-4-2-1 BCD digits. Data from the PCU is represented in program memory as a three digit octal number from 000 to 377.

#### FIGURE 8. Front Panel Indicators.

#### SECTION 5. MAINTENANCE

5-1. GENERAL. This section contains procedures for Performance Verification.

5-2. REQUIRED TEST EQUIPMENT. Recommended test equipment is given in Table 5-1. Test equipment other than recommended may be substituted if specifications equal or exceed the stated characteristics.

5-3. PERFORMANCE VERIFICATION. Use the following procedures to verify basic operation of the instrument (apart from any other component of the Keithley System 1 except the PCU). If the instrument is out of specification at any point, perform the troubleshoot-ing check as in Section 5-4. In addition to test equipment a series 7810 I/O Handler Software program will be needed.

#### TABLE 5-1.

#### Recommended Test Equipment Accessories Needed For Performance Verification

| ltem | Name                                            | Specification                                                                                            | Mfr.      | Model          |  |

|------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------|----------------|--|

| A    | Oscilloscope .                                  | DC coupled, 4 channels, 2V & 5V/div.<br>Sweep rate 50ms/div to 5µs/div<br>External Triggering Capability | Tektronix | 560            |  |

| 8    | Programmable Calcu-<br>lating Unit              | -ll Memory installed (minimum size)                                                                      | KI        | PCU            |  |

| С    | <pre>I/O Handler Software (magnetic card)</pre> | Series 7810                                                                                              | KI        | Series<br>7810 |  |

a. Initial Set-Up

1. Connect the PCU to line power, set Power ON, and set RUN/STEP/LOAD switch to RUN.

2. Set the Control Unit as described in Section 2-6 of this manual.

3. Plug the 37-pin connector from the Control Unit to the rear panel of the PCU.

4. Apply power to the Oscilloscope for measurements to follow. Specific settings will be given for each test.

#### NOTE

Wherever a test point on the circuit board is specified, the circuit designation of the circuit module (such as U103) is given followed by the pin number on that module or integrated circuit (example U103-12).

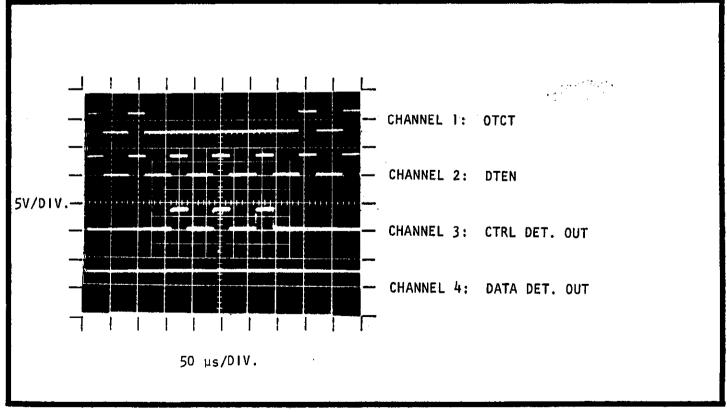

<u>b. Test #1.</u> This test procedure checks the Control/Data Byte Detector under the condition that the PCU is executing no 1/0 instructions. No program is needed for this test.

- 1. Ensure that the PCU is set to ON and that the IDLE light is on.

- 2. Set the oscilloscope as follows:

- a) Vertical Sensitivity 5 volts/div.

- b) Horizontal Sweep 50 µs/div.

- c) Trigger Source Channel 1, positive slope.

- 3. Make connections to the Control Unit circuitry as follows:

- a) Connect Channel | Input to U103-12 (OTCT).

- b) Connect Channel 2 Input to U103-11 (DTEN).

- c) Connect Channel 3 Input to U103-8 (Control Detector output).

- d) Connect Channel 4 Input to U103-9 (Data Detector output).

- 4. Verify that OTCT and DTEN are present as shown in Figure 9.

5. Verify that Control Detector output and Data Detector output are at signal LO as shown in Figure 9.

FIGURE 9. Trace for Test #1.

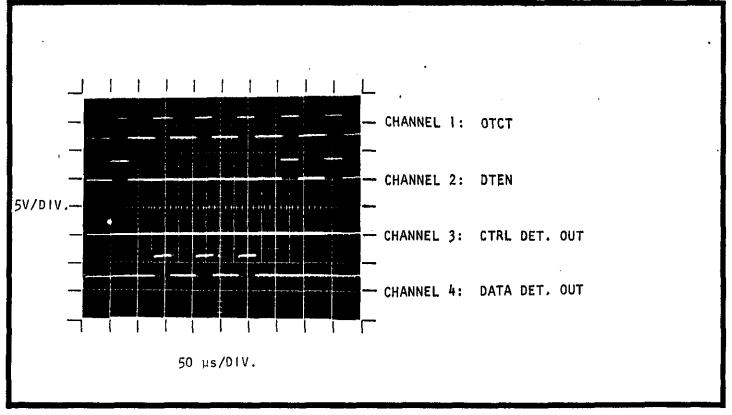

<u>c. Test #2.</u> This test procedure checks the Control/Data Byte Detector outputs under the OPCB condition. A program is needed to obtain the OPCB condition.

- 1. Enter the program listed in Table 5-2. (See page 5-9.)

- 2. Set the RUN/STEP/LOAD switch on the PCU to RUN.

- 3. Set the Oscilloscope as follows:

- a) Vertical Sensitivity 5 volts/div.

- b) Horizontal Sweep 50 µs/div.

- c) Trigger Source Channel 1, positive slope.

4. Make connections to the Control Unit circuitry as follows:

- a) Connect Channel 1 Input to U103-12 (OTCT).

- b) Connect Channel 2 Input to U103-11 (DTEN).

- c) Connect Channel 3 Input to U103-8 (Control Detector output).

- d) Connect Channel 4 Input to U103-9 (Data Detector output).

- 5. Run the program beginning at branch point 0 0.

6. Verify that OTCT is present except during each execution of an OPCB instruction (three consecutive OPCB instructions as in this example), as shown in Figure 10.

7. Verify that DTEN is present regardless of an OPCB instructions.

8. Verify that the Control Detector output goes to Logic "1" during each execution of an OPCB instruction.

FIGURE 10. Trace For Test #2.

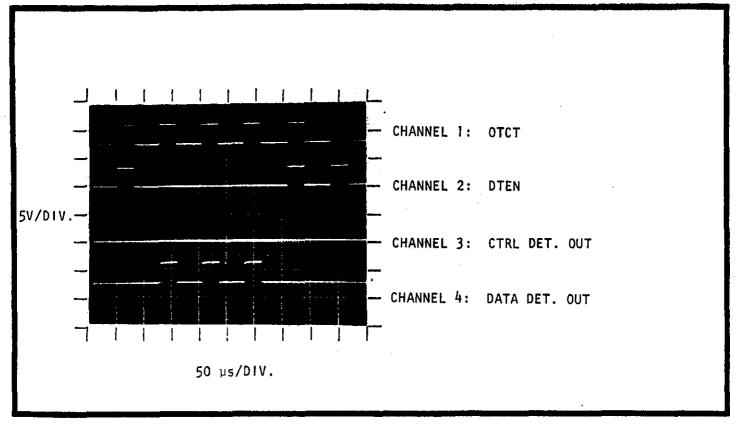

<u>d. Test #3.</u> This test procedure checks the Control/Data Byte Detector outputs under the OPDB condition. A program is needed to obtain the OPCB condition.

- 1. Enter the program listed in Table 5-3. (See page 5-9.)

- 2. Set the RUN/STEP/LOAD switch on the PCU to RUN.

3. Set the Oscilloscope as follows:

- a) Vertical Sensitivity 5 volts/div.

- b) Horizontal Sweep 50µs/div.

- c) Trigger Source Channel 2, positive slope.

4. Make connections to the Control Unit circuitry as follows:

- a) Connect Channel 1 Input to U103-12 (OTCT).

- b) Connect Channel 2 Input to Ul03-11 (DTEN).

- c) Connect Channel 3 Input to U103-8 (Control Detector output).

- d) Connect Channel 4 Input to U103-9 (Data Detector output).

5. Run the program beginning at branch point 0 0.

6. Verify that DTEN is present except during each execution of a OPDB instruction (three consecutive OPDB instructions as in this example), as shown in Figure 11.

7. Verify that OTCT is present regardless of a OPDB instruction.

8. Verify that the Data Detector output goes to Logic "1" during each execution of a OPDB instruction.

FIGURE 11. Trace for Test #3.

<u>e. Test #4.</u> This test procedure checks the Control/Data Byte Detector outputs under the IPDB condition. A program is needed to obtain the IPDB condition.

- 1. Enter the program listed in Table 5-4. (See page 5-9.)

- 2. Set the RUN/STEP/LOAD switch on the PCU to RUN.

- 3. Set the oscilloscope as follows:

- a) Vertical Sensitivity 5 volts/div.

- b) Horizontal Sweep 50µs/div.

- c) Trigger Source Channel 2, positive slope.

4. Make connections to the Control Unit circuitry as follows:

- a) Connect Channel | Input to U103-12 (OTCT).

- b) Connect Channel 2 Input to U103-11 (DTEN).

- c) Connect Channel 3 Input to U103-8 (Control Detector output)

- d) Connect Channel 4 Input to Ul03-9 (Data Detector output)

- 5. Run the program beginning at branch point 0 0.

6. Verify that DTEN is present except during each execution of a IPDB instruction (three consecutive IPDB instructions as in this example), as shown in Figure 12.

7. Verify that OTCT is present regardless of a IPDB instruction.

8. Verify that the Data Detector output goes to Logic "1" during each execution of a IPDB instruction.

FIGURE 12. Trace for Test #4.

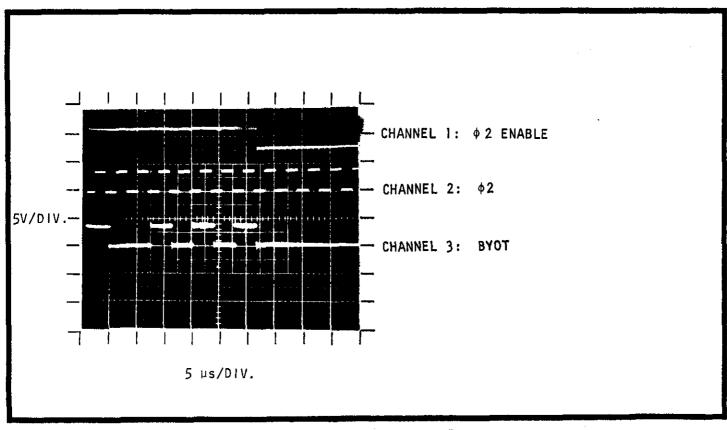

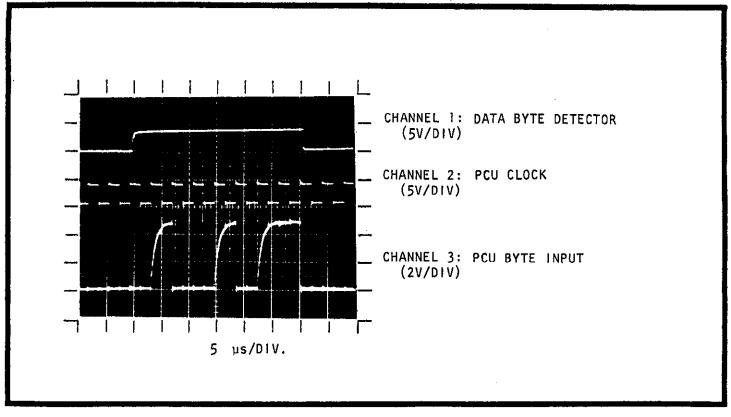

<u>f. Test #5.</u> This test procedure checks the  $\phi$ 2 Enable Line. The  $\phi$ 2 Enable line, PCU clock line, and PCU BYOT line are used to control the operation of the Output Control/Data Register. A program must be loaded into the PCU to obtain an OPCB condition.

- 1. Enter the program as listed in Table 5-5. (See page 5-9.)

- 2. Set the RUN/STEP/LOAD switch on the PCU to RUN.

- 3. Set the Oscilloscope as follows:

- a) Vertical Sensitivity 5 volts/div.

- b) Horizontal Sweep 5µs/div.

- c) Trigger Source Channel 1, positive slope.

- 4. Make connections to the Control Unit circuitry as follows:

- a) Connect Channel | Input to U107-10 (\$2 Enable).

- b) Connect Channel 2 Input to U107-9 ( $\phi$ 2).

- c) Connect Channel 3 Input to Ullo-1 (BYOT, Data Out)

- 5. Run the program beginning at branch point 0 0.

- 6. Verify the traces shown in Figure 13.

#### NOTES.

Data is clocked into the Output Control/Data Register on the falling edge of  $\phi 2$ . Data is clocked with LI being sent first. LI to H8 is 10010101 binary.

FIGURE 13. Trace for Test #5.

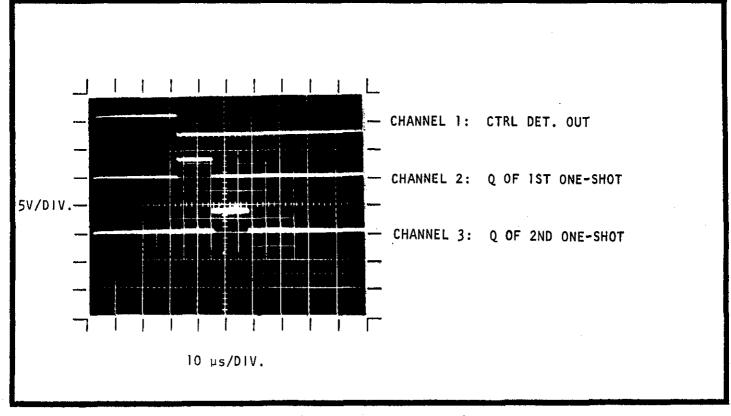

<u>g. Test #6.</u> This test procedure checks the relationship between: Control Byte Detector Output and the two one shots associated with Control Bytes under the OPCB condition. A program must be loaded into the PCU to obtain the OPCB condition.

- 1. Enter the program listed in Table 5-6. (See page 5-9.)

- 2. Set the RUN/STEP/LOAD switch on the PCU to RUN.

- 3. Set the Oscilloscope as follows:

- a) Vertical Sensitivity 5 volts/div.

- b) Horizontal Sweep 10µs/div.

- c) Trigger Source Channel 1, positive slope.

4. Make connections to the Control Unit circuitry as follows:

- a) Connect channel | Input to UI03-8 (Control Byte Detector output).

- b) Connect Channel 2 Input to U131-6 (Q output of 1st one-shot).

- c) Connect Channel 3 Input to U132-6 (Control Pulse CP)

- 5. Run the program beginning at branch point 0 0.

6. Verify the traces shown in Figure 14.

a) Q output of first one-shot should coincide with Logic "1" to Logic "0" transition of the Control Byte Detector output. (Synchronizes signals for the Control Unit.)

b) Q output of second one-shot should coincide with Logic "1" to Logic "0" transition of Q output of first one-shot. (Synchronizes control signals for Ins-trument Interfaces.)

FIGURE 14. Trace For Test #6.

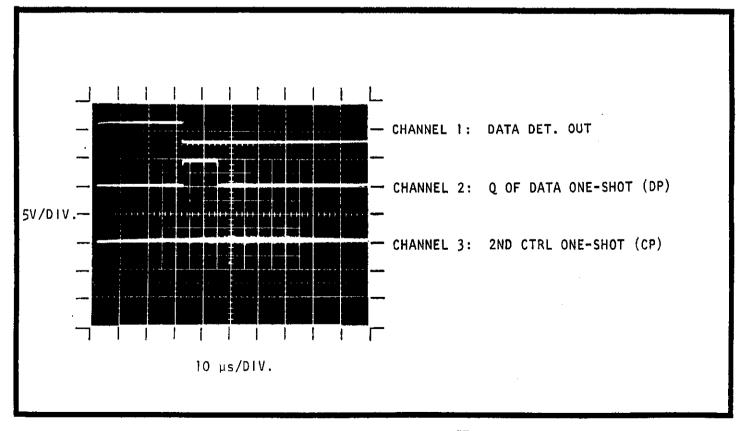

h. Test #7. This test procedure checks the relationship between: Data Byte Detector Output and the Data Pulse (DP) one-shot under the OPDB condition. A program must be loaded into the PCU to obtain the OPDB condition.

- 1. Enter the program listed in Table 5-7. (See page 5-9.)

- 2. Set the RUN/STEP/LOAD switch on the PCU to RUN.

- 3. Set the Oscilloscope as follows:

- a) Vertical Sensitivity 5 volts/div.

- b) Horizontal Sweep 10µs/div.

- c) Trigger Source Channel 1, positive slope.

- 4. Make connections to the Model 780 circuitry as follows:

- a) Connect Channel 1 Input to U103-9 (Data Byte Detector output).

- b) Connect Channel 2 Input to U128-14 (Data Pulse DP).

- c) Connect Channel 3 Input to U132-6 (Control Pulse CP).

- 5. Run the program beginning at branch point 0 0.

- 6. Verify the traces shown in Figure 15.

a) Data Pulse should coincide with the Logic "1" to Logic "0" transition of the Byte Detector Output.

b) Control Pulse does not appear (remains at Logic "0").

FIGURE 15. Trace For Test #7.

|                 | Table 5-2 |     |    |      |             |           |                         |      |    |  |  |  |  |

|-----------------|-----------|-----|----|------|-------------|-----------|-------------------------|------|----|--|--|--|--|

|                 | Pro       | ogr | am | Need | ed          | to        | Perform                 | Test | #2 |  |  |  |  |

| DECIMAL<br>STEP |           |     |    |      | RUC<br>Codi | TION<br>E | INSTRUCTION<br>MNEMONIC |      |    |  |  |  |  |

| 0               | 0         | 0   | 0  | 3    | 1           | 4         | OPCB                    |      |    |  |  |  |  |

|                 |           |     | 1  | 3    | 1           | 4         | OPCB                    |      |    |  |  |  |  |

|                 |           |     | 2  | 3    | 1           | 4         | OPCB                    |      |    |  |  |  |  |

|                 |           |     | 3  | 2    | 2           | 0         | JU00,                   | 000  |    |  |  |  |  |

|                 |           |     | 4  | 0    | 0           | 0         |                         |      |    |  |  |  |  |

| Table | 5-3 |

|-------|-----|

|-------|-----|

|                 | F | °ro | gra       | m Ne        | ede | ed to | Perfo                   | rm Test #3 |  |

|-----------------|---|-----|-----------|-------------|-----|-------|-------------------------|------------|--|

| DECIMAL<br>STEP |   |     | inst<br>( | RUC<br>Code | -   |       | INSTRUCTION<br>MNEMONIC |            |  |

| 0               | 0 | 0   | 0         | 3           | 1   | 5     | OPDB                    | ,          |  |

|                 |   |     | 1         | 3           | 1   | 5     | OPDB                    |            |  |

|                 |   |     | 2         | 3           | 1   | 5     | OPDB                    |            |  |

|                 |   |     | 3         | 2           | 2   | 0     | JU00,                   | 000        |  |

|                 |   |     | 4         | 0           | 0   | 0     |                         |            |  |

Table 5-4

|   | ſ          | Program Needed to |            |   |   |                         |  | Perfor | m  | Test | #4 |

|---|------------|-------------------|------------|---|---|-------------------------|--|--------|----|------|----|

|   | DECI<br>St | INST<br>C         | RUC<br>Ode |   | N | INSTRUCTION<br>MNEMONIC |  |        |    |      |    |

| 0 | 0          | 0                 | 0          | 3 | 0 | 5                       |  | IPDB   |    |      |    |

|   |            |                   | 1          | 3 | 0 | 5                       |  | IPDB   |    |      |    |

|   |            |                   | 2          | 3 | 0 | 5                       |  | IPDB   |    |      |    |

|   |            |                   | 3          | 2 | 2 | 0                       |  | JU00,  | 00 | 10   |    |

|   |            |                   | 4          | 0 | 0 | 0                       |  |        |    |      |    |

| TABL | Ε 5 | 5-5. |

|------|-----|------|

|------|-----|------|

|   | Pro       | o g i      | ram    | Nee    | ede        | эd     | To Perform Test #5        |

|---|-----------|------------|--------|--------|------------|--------|---------------------------|

|   | DEC<br>S1 | IMA<br>Fep | L      | INST   | RUC<br>COD |        | N INSTRUCTION<br>MNEMONIC |

| 0 | 0         | 0          | 0      | 2      | 6          | 6      | LDIX, 251                 |

|   |           |            | 1      | 2      | 5          | 1      |                           |

|   |           |            | 2      | 3      | 1          | 4      | ОРСВ                      |

|   |           |            | 3<br>4 | 2<br>0 | 2<br>0     | 0<br>0 | JU00, 000                 |

|  | TABLE | 5-6. |

|--|-------|------|

|--|-------|------|

|   |   | Pro        | gra | am Ne | ed          | ed | То | Perfor         | m Test #6               |

|---|---|------------|-----|-------|-------------|----|----|----------------|-------------------------|

|   |   | IMA<br>Fep | L   | INS   | TRU(<br>COD |    | N  |                | INSTRUCTION<br>MNEMONIC |

| 0 | 0 | 0          | 0   | 2     | 6           | 6  |    | LDIX,          | 251                     |

|   |   |            | 1   | 2     | 5           | 1  |    |                |                         |

|   |   |            | 2   | 3     | 1           | 4  |    | OPCB           |                         |

|   |   |            | 3   | 2     | 2           | 0  |    | JU <i>00</i> , | 000                     |

|   |   |            | 4   | 0     | 0           | 0  |    |                |                         |

TABLE 5-7.

|   |           | Pro       | og r | am | Νe | eed        | ed     | to | Perfor | m Test #7               |

|---|-----------|-----------|------|----|----|------------|--------|----|--------|-------------------------|

|   | DEC<br>S1 | IMA<br>EP | L    | 11 |    | RUC<br>Cod | E<br>E | N  |        | INSTRUCTION<br>MNEMONIC |

| 0 | 0         | 0         | 0    |    | 2  | 6          | 6      |    | LDIX,  | 015                     |

|   |           |           | 1    |    | 0  | 1          | 5      |    |        |                         |

|   |           |           | 2    |    | 3  | 1          | 5      |    | OPDB   |                         |

|   |           |           | 3    |    | 2  | 2          | 0      |    | JU00,  | 002                     |

|   |           |           | 4    |    | 0  | 0          | 2      |    |        |                         |

.

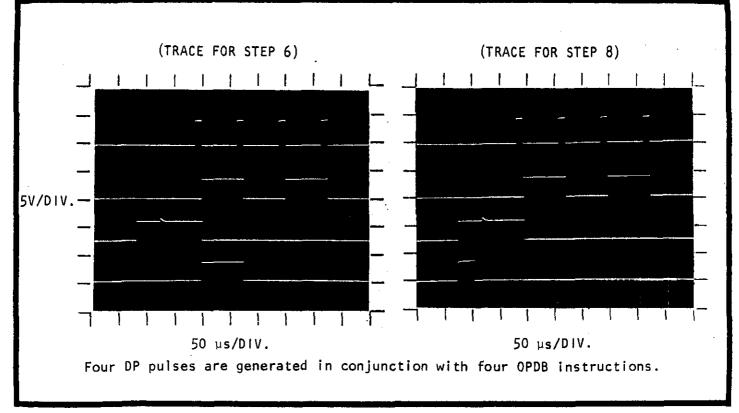

<u>i. Test #8.</u> This test procedure checks the Data Output Register and the Data Output lamp drivers. A series 7810 1/0 Handler program (magnetic card) is needed to perform the test, as well as a specific keyboard entered program.

1. Enter a series 7810 I/O Handler program via the magnetic card reader at branch point 0 0.

2. Enter the program listed in Table 5-8. (See page 5-13.)

3. Place the PCU in Program Mode.

4. Run the program beginning at branch point 0 0.

5. Verify that the Data Output indicators (representing DOL1, DOL2, DOL4, DOL8, DOH1, DOH2, DOH4, DOH8) are lighted corresponding to a "walking one" moving towards the left. The Data Output lines DOL1 through DOL8 may also be observed. Since the data lines are inverted, a "walking zero" should be observed.

6. Enter the program listed in Table 5-9.

7. Place the PCU in Program Mode.

8. Run the program beginning at branch point 0 0.

9. Verify that the Data Output indicators (representing DOL1, DOL2, DOL4, DOL8, DOH1, DOH2, DOH4, DOH8) are lighted corresponding to a "walking zero" moving towards the left. The Data Output lines, DOL1 through DOH8 may also be observed. Since the data lines are inverted, a "walking one" should be observed.

j. Test #9. This test procedure checks the Byte Counter circuitry using a static test. A program must be loaded into the PCU to obtain OPCB and OPDB conditions.

1. Enter the program listed in Table 5-10. (See page 5-13.)

2. Place the PCU in Program mode.

3. Set the oscilloscope as follows:

- a) Vertical Sensitivity 2 volts/div.

- b) Horizontal Sweep 50 ms/div.

- c) Trigger Source AUTO Trigger.

4. Make connections to the following Byte Count (BC) lines at Interface Number 1: BCO, BC1, BC2, BC3, BC4, BC5, BC6, BC7.

5. Run the program beginning at branch point 0 0.

6. Verify that the BCO line is at Logic "I" when the PCU "IDLE" indicator is lighted.

7. Depress RESUME.

8. Verify that BCl line is at Logic "1" when the PCU "IDLE" indicator is lighted.

9. Depress RESUME.

10. Verify that BC2 line is at Logic "1" when the PCU "IDLE" indicator is lighted.

NOTE

Continue the test in a similar fashion until BC7 has been tested. Each time RESUME is depressed the program will cause the next BC line to go to Logic "l". After BC7 has been tested, all succeeding RESUME key strokes will have no effect on the BC lines (that is, all BC lines will remain at Logic "O"). The program may be run again by jumping to branch point 0 0.

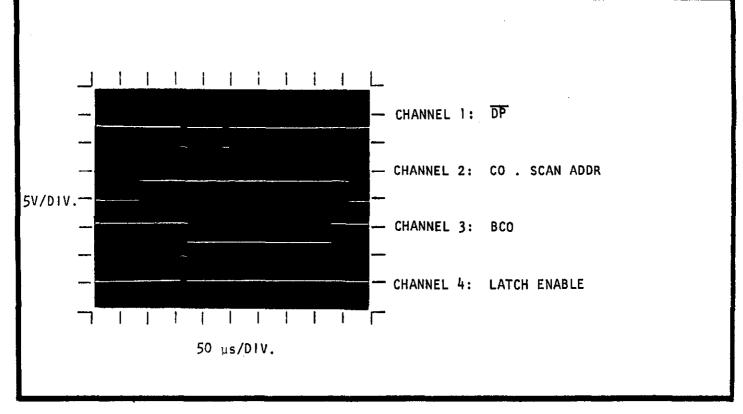

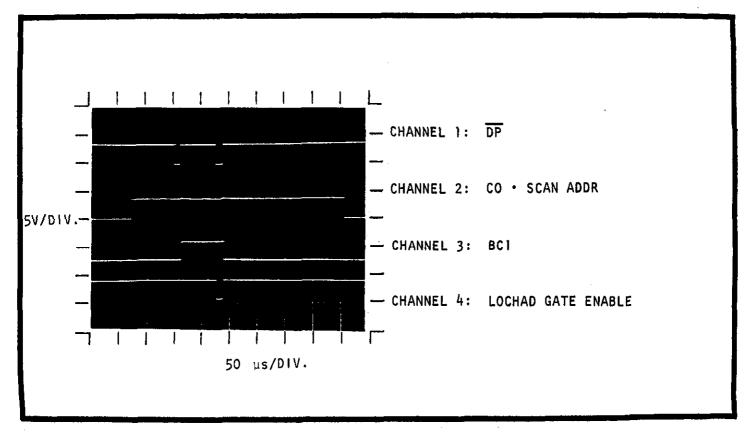

k. Test #10. This procedure checks the Byte Counter circuitry using a dynamic test. A program must be loaded into the PCU to obtain OPCB and OPDB conditions.

- 1. Enter the program listed in Table 5-11. (See page 5-13.)

- 2. Set the RUN/STEP/LOAD switch on the PCU to RUN.

- 3. Set the oscilloscope as follows:

- a) Vertical Sensitivity 5 volts/div.

- b) Horizontal Sweep DELAYED 50µs/div.

- c) Trigger Source Channel 1, positive slope.

4. Make connections to the Control Unit circuitry as follows:

- a) Connect Channel 7 input to U128-14 (Data Pulse DP).

- b) Connect Channel 2 input to U128-1 (QA on Data Byte Counter).

- c) Connect Channel 3 input to U105-2 (BC0).

- d) Connect Channel 4 input to U105-4 (BC1).

- 5. Run the program beginning at branch point 0 0.

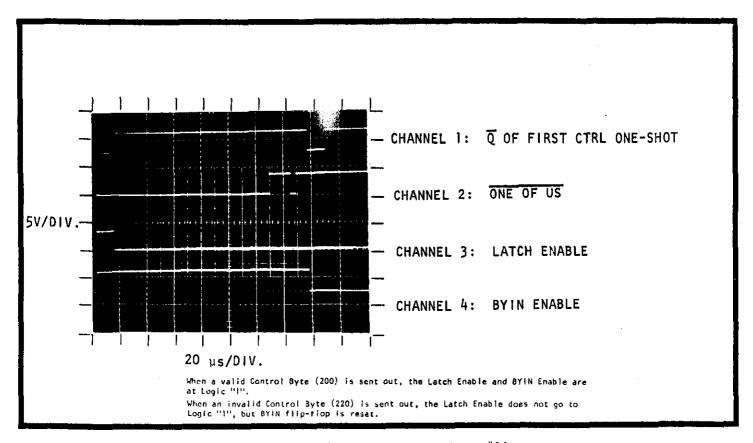

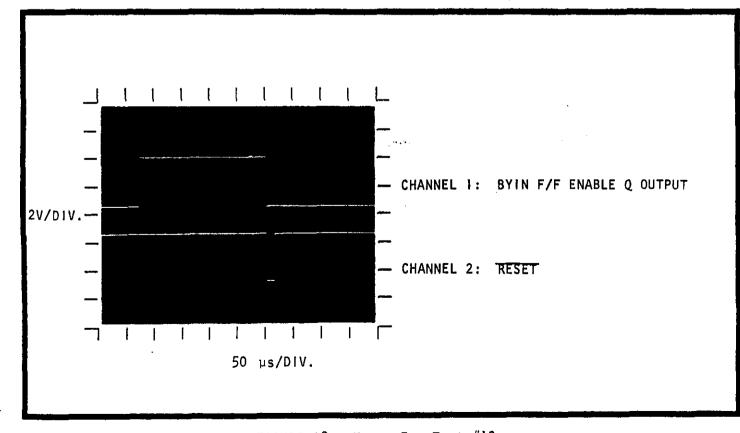

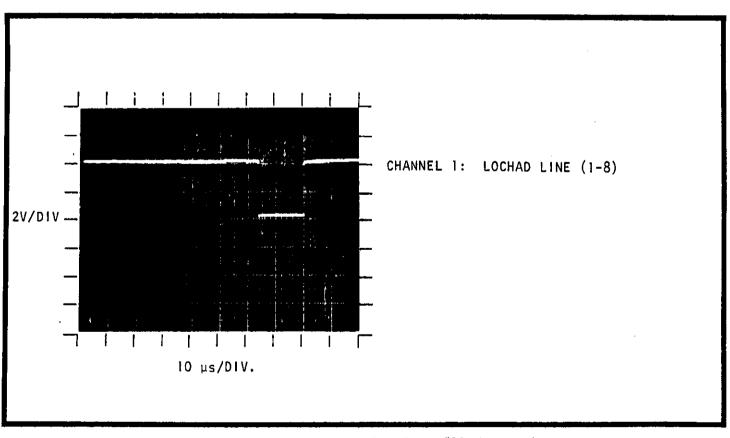

6. Verify that QA is toggled by the Logic "1" to Logic "0" transition of the Data Pulse (DP), thus incrementing the Byte Counter from BCO to BC1.